|

Neuromorphic Hardware

|

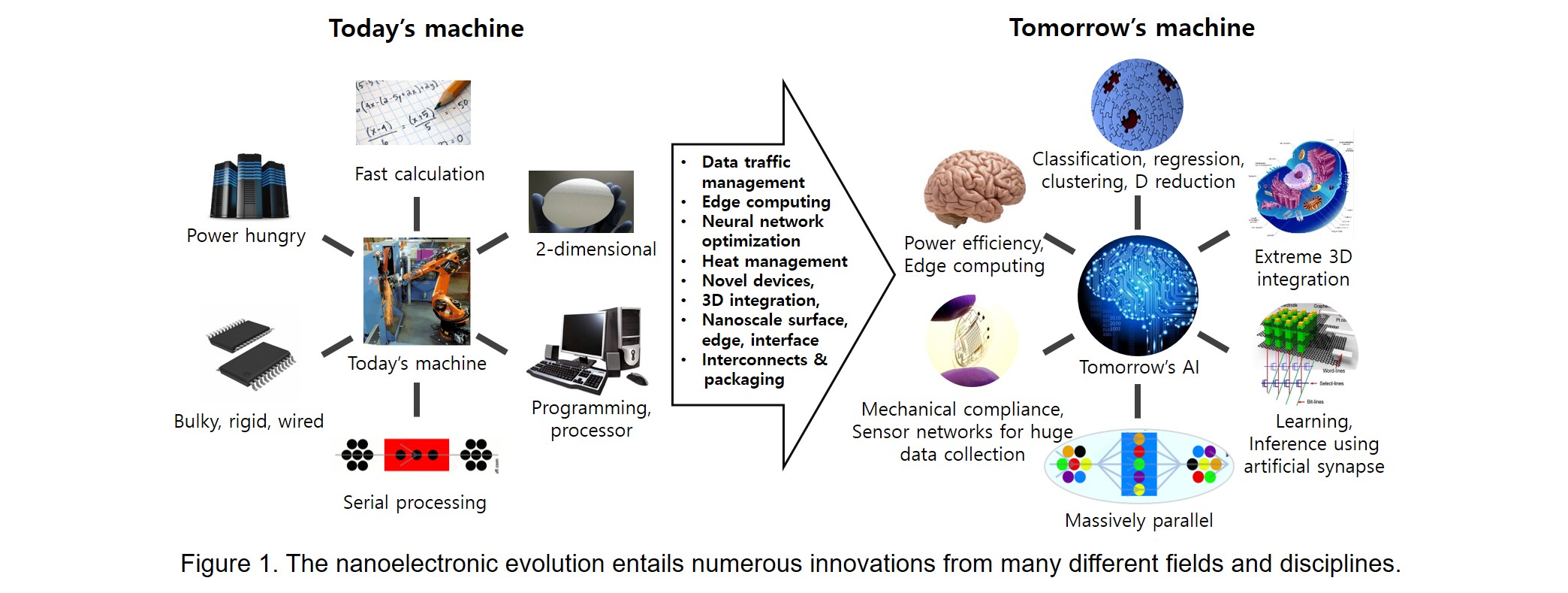

Understanding the mechanisms of neural information processing is crucial for the ultimate creation of artificial intelligence. Compared to today’s limited computation systems, the brain is characterized by parallelism, plasticity, ultra-high density and low energy consumption. Synaptic clusters which dominate the architecture of the brain are essential for biological computations that regulate the cognitive learning and perception. In our group, we aim to develop nanoscale device arrays which emulate the functions and plasticity of the synaptic clusters and ultimately create an artificial neural network. Our goal is to investigate brain-inspired architectures and self-learning systems to address the inherent limitations of today’s computation systems.

|

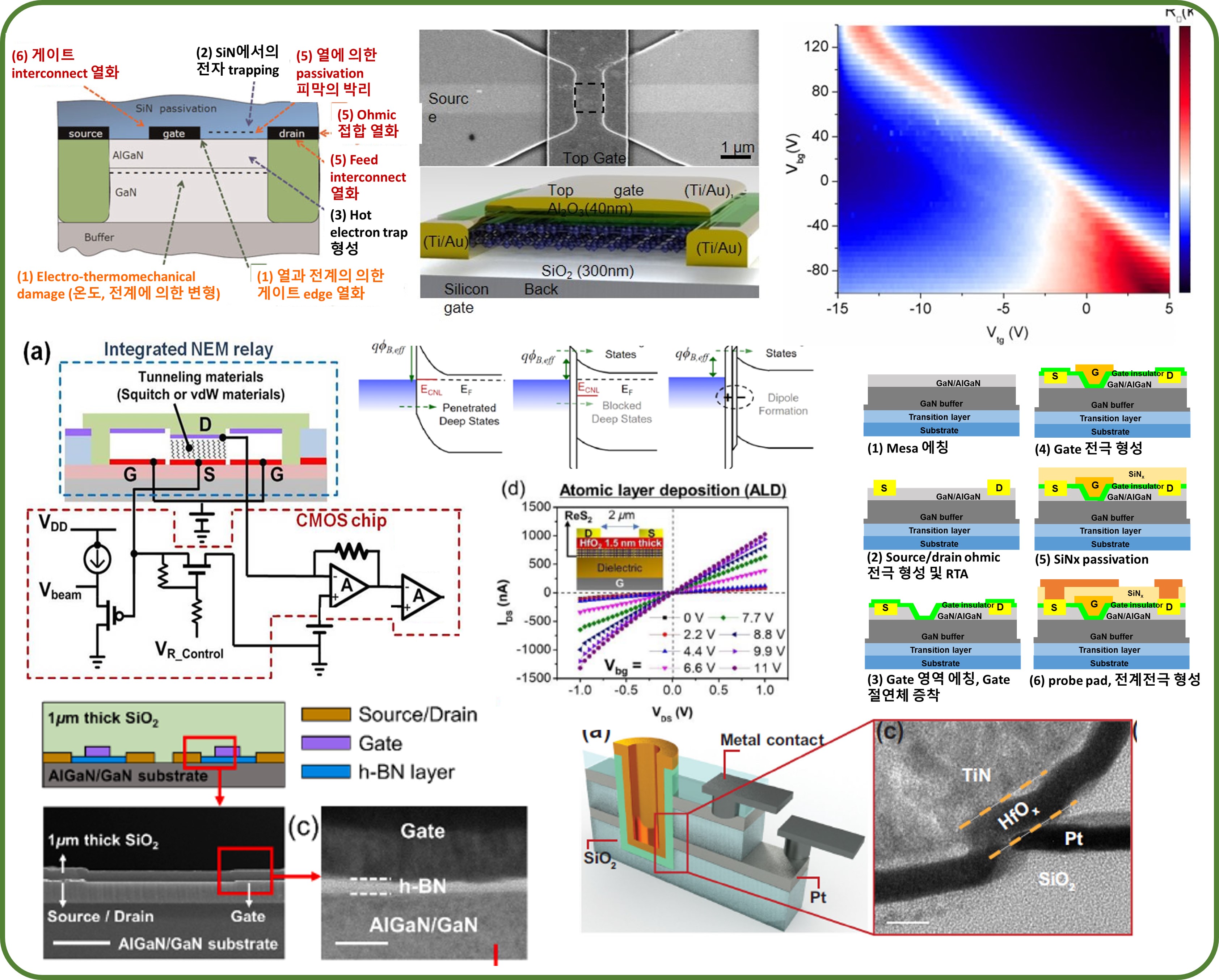

At Stanford, one of my research efforts was to develop an extremely low power, non-volatile memory that utilized atomically thin edges of graphene as one of the electrodes. Compared to the same architecture that uses conventional metal (Pt) as an electrode, the atomically thin graphene edge electrode was able to reduce power consumption by ×300 while producing a highly localized electrical field for oxygen anion migration. The switching energy of this device is one of the lowest reported compared to existing alternative memory technologies. The increased density and the low power consumption of this memory structure will enable significant progress in emerging application areas such as energy-efficient abundant-data computing and neuromorphic computing. Memories employing various oxides have already been demonstrated for spike-timing-dependent plasticity. A highly integrated electronic synapse network employing low-power graphene memory in a bit-cost-effective 3D architecture will be a significant step towards a highly efficient, next-generation neuromorphic system. |

Current applications of interest include:

Hardware implementation of convolutional neural network

Heat management in neuromorphic memristor arrays

Ultralow power artifical neurons in vertical cross-point architecture

Related Publications

Seunghyun Lee, Sanghoek Kim, ‘‘Power Link Optimization for a Neurostimulator in Nasal Cavity" , submitted

Seunghyun Lee, Joon Sohn, Zizhen Jiang, Hong-Yu Chen, and H. -S. Philip Wong, ‘‘Metal Oxide Resistive Memory using Graphene Edge Electrode", Nature Communications 6, 8407 (2015).

Ahn, Chiyui, Scott W. Fong, Yongsung Kim, Seunghyun Lee, Aditya Sood, Christopher M. Neumann, Mehdi Asheghi, Kenneth E. Goodson, Eric Pop, and H-S. Philip Wong. ‘‘Energy-efficient phase-change memory with graphene as a thermal barrier", Nano Letters 15, no. 10 (2015): 6809-6814.

Zhang, Weixia, Sudarat Lee, Kelly L. McNear, Ting Fung Chung, Seunghyun Lee, Kyunghoon Lee, Scott A. Crist et al. “Use of graphene as protection film in biological environments.” Scientific reports 4 (2014).

Seunghyun Lee, Zhaohui Zhong, ‘‘Nanoelectronic circuits based on two-dimensional atomic layer crystals", Nanoscale, 6(22) 13283-13300. (2014)

Seunghyun Lee, Joon Sohn (co-1st author), Zizhen Jiang, Hong-Yu Chen and H.-S. Philip Wong, ‘‘Atomically Thin Graphene Plane Electrode for 3D RRAM", IEDM, paper 5.3, pp. 116-119, (2014)

Yang, Yuchao, Jihang Lee, Seunghyun Lee, CheHung Liu, Zhaohui Zhong, and Wei Lu. ‘‘Oxide Resistive Memory with Functionalized Graphene as Built?in Selector Element", Advanced Materials 26, no. 22 (2014): 3693-3699